# Работа в JTAG Maps для Altium Designer

Алексей Иванов (alexey@jtag.com)

**В статье описывается процесс работы с расширением JTAG Maps для пакета проектирования электронных устройств и плат Altium Designer. Программа JTAG Maps позволяет разработчику схем уже на этапе проектирования оценить возможность доступа периферийного (границочного) сканирования к цепям.**

При разработке электронных устройств необходимо обеспечить их правильное функционирование в будущем, исключить проблемы, связанные со сборкой (как правило, это означает разработать плату под автоматический SMD-монтаж), обеспечить надёжность, защищённость от внешних воздействий и многое другое. Должное соблюдение перечисленных требований позволит разработать и создать современный конкурентно-способный продукт. Большинство из этих задач решаются инженерами-проектировщиками в САПР в процессе создания схемы и разводки печатной платы. Такой САПР может являться, например, Altium Designer.

В современных условиях немаловажно разработать, в том числе, и тестопригодное изделие. Опыт показывает, часто уникальные, нужные приборы со сложнейшей функциональностью, востребованные рынком и потребителями, оказываются непригодными к серийному выпуску по причине отсутствия

возможности их структурного тестирования на производстве. Их попросту невозможно произвести из-за сложности диагностики дефектов монтажа. Для диагностики таких сложных цифровых плат уже десятки лет существует технология периферийного сканирования. Программная утилита JTAG Maps от JTAG Technologies и Altium позволяет разработчику ещё на этапе составления схемы понять, насколько его будущая плата будет тестируема с помощью периферийного сканирования.

Очевидно, что самым первым фактором, которому необходимо уделить внимание ещё до начала использования JTAG Maps, является выбор центральных компонентов платы (процессоры, контроллеры, ПЛИС) с поддержкой стандарта периферийного сканирования IEEE 1149.1. Именно за счёт этих компонентов впоследствии будет производиться сканирование цепей платы. При этом необходимо обеспечить доступ тестового оборудования к интерфейсам JTAG. После

того как компоненты с поддержкой периферийного сканирования выбраны, наступает черёд разработки схемы изделия. На данном этапе тестопригодность будущего изделия будет контролироваться с помощью JTAG Maps.

Для того чтобы установить это бесплатное расширение, необходимо открыть Altium Designer и зайти в меню DXP. Затем выбрать «Extensions and Updates» и «Purchased but not installed». В открывшемся окне поиска набрать «JTAG Maps». В результатах поиска необходимо выбрать иконку JTAG Maps и нажать кнопку «Install». После завершения установки кнопка запуска программы будет находиться в правом нижнем углу Altium Designer. При нажатии на неё откроется окно программы JTAG Maps (см. рис. 1). Анализ тестопригодности платы начинается с нажатия кнопки «Start», но при первом запуске будет предложено загрузить файл бесплатной лицензии с сайта JTAG Technologies. Лицензия привязывается к MAC-адресу компьютера. В Altium Designer необходимо будет указать путь к скачанному на данном этапе бесплатному лицензионному файлу, зайдя в «Preferences» – «JTAG Maps».

После того как лицензия установлена, можно вновь нажимать кнопку «Start» – откроется окно для ввода исходных

Рис. 1. Интерфейс программы JTAG Maps

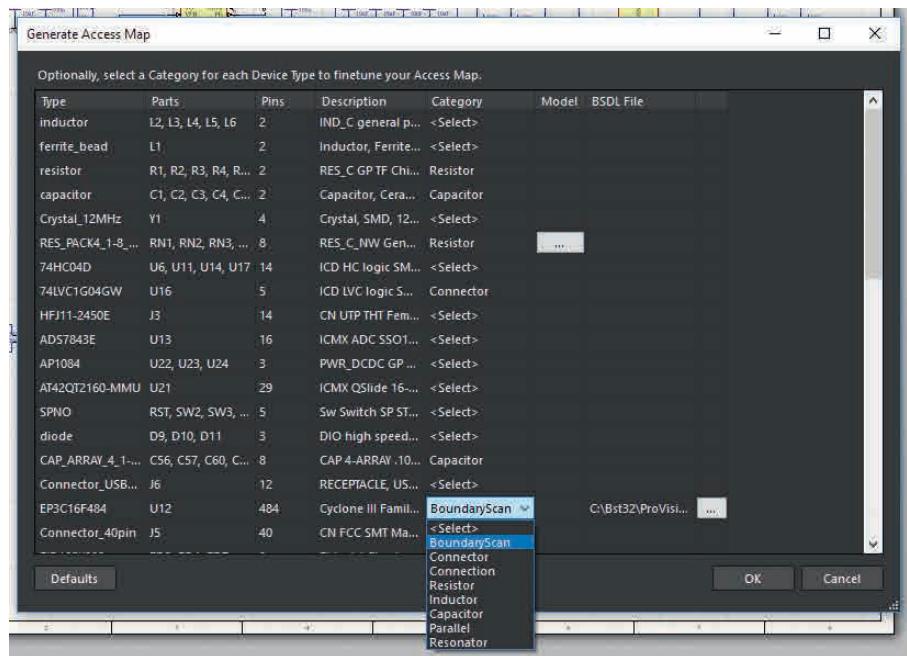

Рис. 2. Присвоение компоненту атрибута «BoundaryScan»

данных для анализа тестопригодности. Сама по себе система Altium не знает, какие компоненты поддерживают периферийное сканирование, какие элементы являются «прозрачными» для тестовых сигналов (например, резисторы), поэтому необходимо ввести соответствующие базовые данные. Как показано на рисунке 2 компоненту можно присвоить следующие атрибуты: «BoundaryScan» (компонент с поддержкой периферийного сканирования), Connector (разъём), Connection (есть возможность прохождения через элемент тестовых сигналов), Resistor, Inductor, Capacitor, Parallel (может рассматриваться как место подключения внешнего тестового оборудования), Resonator. При этом для различных категорий можно выбрать разные электрические модели, например, резистор превратить в резистивную сборку, указав таблицу соединений.

Для определения функциональности компонентов с поддержкой периферийного сканирования в JTAG Maps есть два варианта: приблизительный и точный. Первый вариант предусматривает присвоение компонен-

ту статуса «BoundaryScan», тогда все выводы микросхемы, кроме питания и земли, будут считаться полностью сканируемыми, работающими во время JTAG-теста платы как вход/выход (IO). Но в реальности поведение выводов микросхем при периферийном сканировании не всегда однозначное и зависит от конкретного типа ИМС. Некоторые выводы будут действительно являться входами/выходами, другие – односторонними, а какие-то из сигнальных портов вообще не будут иметь в своём составе ячеек периферийного сканирования. Вся эта информация предоставляется производителем микросхемы в виде BSDL-файла (BoundaryScan Description Language). Эти файлы, как правило, скачиваются с сайта производителя микросхемы, либо запрашиваются у него напрямую. При наличии BSDL-файла можно подставить его в окно ввода исходных данных для расчёта (например, для микросхемы U12 на рисунке 2). Очевидно, что при таком подходе тестовый доступ будет показан более точно, нежели если просто сообщить системе, что

компонент имеет поддержку периферийного сканирования.

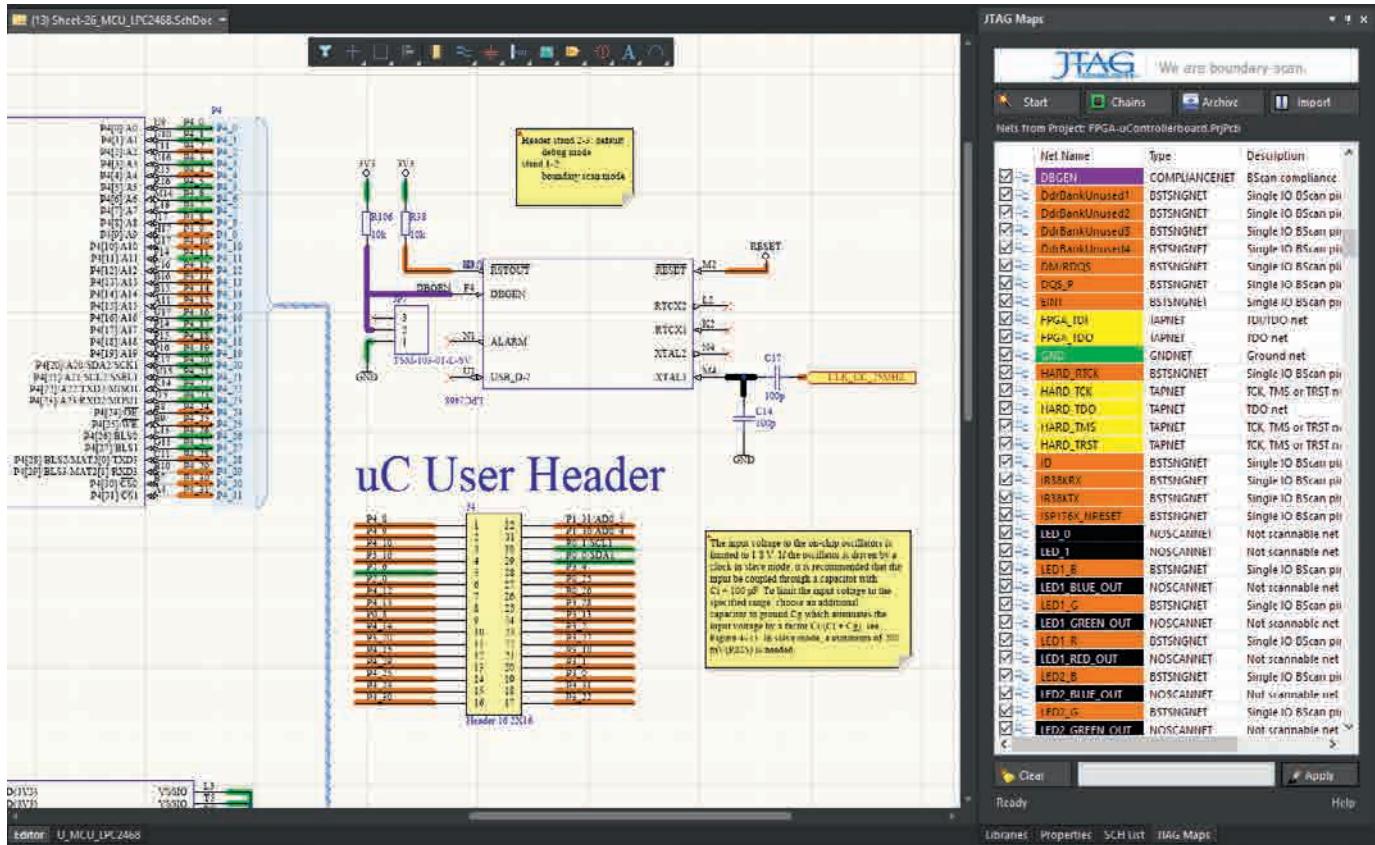

После определения атрибутов для компонентов платы необходимо их применить, нажав кнопку «OK» (см. рис. 2), после чего в окне JTAG Maps будут отображены цепи исследуемой платы, подсвеченные разными цветами (см. рис. 3). Помимо красного цвета, обозначающего цепи питания и земли, в списке можно увидеть цепи, обозначенные зелёным цветом, оранжевым, жёлтым и чёрным.

Зелёным цветом показываются цепи «fully scanable», это означает, что все выводы компонентов, подключённых к ним, имеют поддержку периферийного сканирования. Для таких цепей тестирование возможно в наиболее полном объёме. Они могут располагаться, например, между ПЛИС и процессором, между различными ПЛИС и т.д.

Оранжевым цветом отмечаются цепи, в которых содержатся драйверы и/или сенсоры с поддержкой периферийного сканирования, но также имеются выводы компонентов без неё (т.н. «клUSTERы»). Эти цепи, возмож-

[www.jtagtechnologies.ru](http://www.jtagtechnologies.ru)

**JTAG ProVision** – самая совершенная программа для периферийного сканирования на сегодняшний день

Автоматическая генерация тестов

Русскоязычный интерфейс

Скрипты для создания продвинутых тестов

Десятки тысяч готовых моделей ЭКБ

Последовательности для производства

Проверена работа с отечественной ЭКБ, поддерживающей периферийное сканирование!

Представительство JTAG Technologies в России

Телефон: (812) 602-0915

E-mail: russia@jtag.com

Эксклюзивный дистрибутор: ООО «Остек-Электро»

Телефон: (495) 788-4444

E-mail: info@ostec-group.ru

**Рис. 3. Внешний вид окна JTAG Maps с разноцветными цепями исследуемой платы**

но, удастся протестировать с помощью кластерного теста, но JTAG Maps не имеет моделей функциональности различных кластеров (ОЗУ, ПЗУ, логика и пр.) и точно просчитать тестируемость таких цепей можно только в профессиональных программах создания приложений для периферийного сканирования, таких как JTAG ProVision.

Чёрным цветом показываются нетестируемые цепи, жёлтым – цепи JTAG-интерфейса (TAP-сигналы).

На данном этапе можно выбрать цепи, которые необходимо подсветить на схеме (или выбрать все) и нажать кнопку «Apply». После этого межсоединения разрабатывающей платы подкрасятся соответствующими цветами (см. рис. 3). Теперь можно наблюдать тестопригодность всей схемы в целом. Если заранее были определены BSDL-файлы для компонентов с поддержкой JTAG, то в ряде случаев на схеме можно увидеть цепи, которые требуют специальных установок для перевода микросхемы в режим периферийного сканирования. Данные установки для некоторых устройств описаны в разделе «COMPLIANCE PATTERNS» BSDL-модели. По умолчанию такие цепи подсвечиваются фиолетовым цветом.

Если обратить внимание на цепи, идущие от компонентов, поддерживающих периферийное сканирование на внешние разъёмы, то можно заметить, что они подсвечены оранжевым цветом, то есть рассматриваются как частично тестируемые. Однако многим инженерам, занимающимся JTAG-тестированием, известно, что такие цепи можно протестировать со 100%-м покрытием, подключив к разъёмам DIOS- или MIOS-модули (модули ввода-вывода). Если предположить, что при производственном JTAG-тестировании разрабатываемого изделия будут использоваться IO-модули, то для разъёмов можно определить атрибут «Parallel». Для этого необходимо вновь нажать кнопку «Start» и внести требуемые изменения, после чего цепи разъёмов, которые были показаны оранжевым цветом, будут «перекрашены» в зелёный.

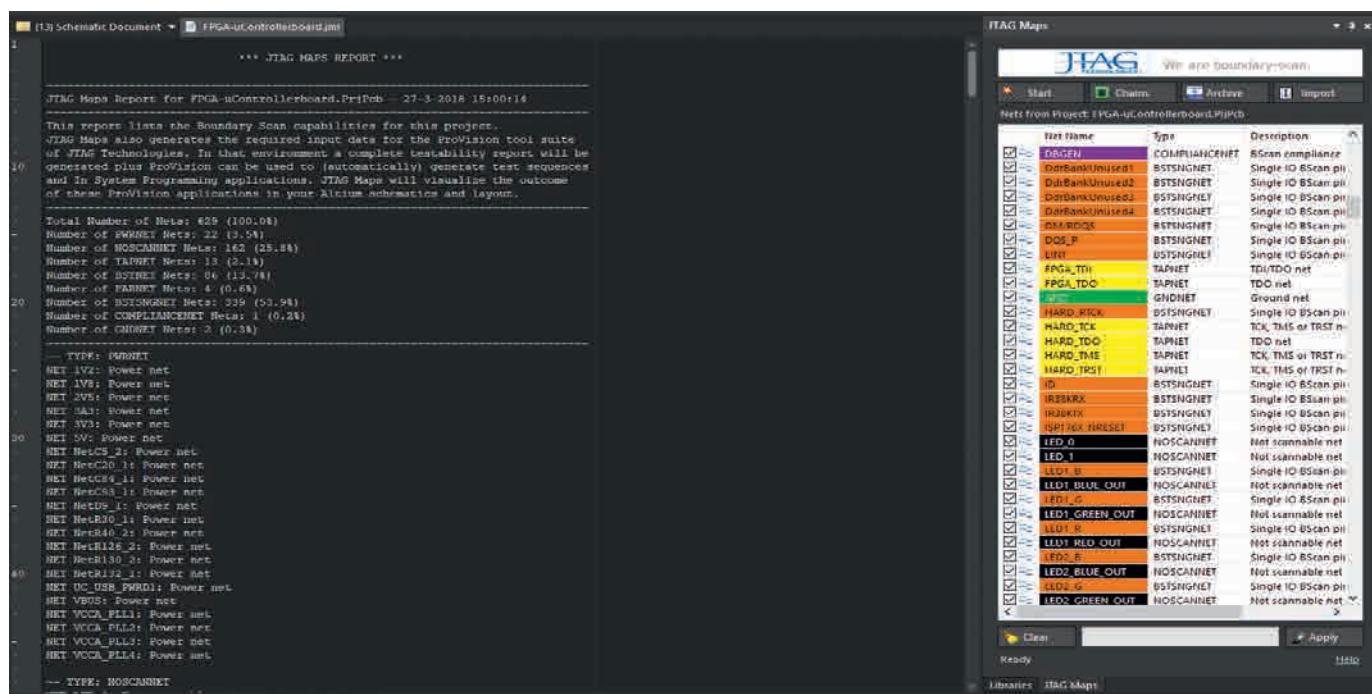

Для того чтобы посмотреть общую статистику по тестовому покрытию, можно кликнуть правой кнопкой мыши на списке цепей в окне JTAG Maps и выбрать «Show report». В открывшемся окне (см. рис. 4) можно увидеть общее количество полностью сканируемых (BSTNET), частично сканируемых (BSTSNGNET), не тестируемых

(NOSCANNET) цепей, линий JTAG-интерфейса (TAPNET). Также в статистическом отчёте присутствует список всех цепей с их признаками тестируемости.

Среди возможностей программы JTAG Maps следует отметить также функцию экспорта архива проекта для среды разработки тестов JTAG ProVision (кнопка «Export» на заглавном окне JTAG Maps). Этот архив может впоследствии быть использован в качестве базы для создания проекта тестирования платы. В JTAG ProVision будет добавлена дополнительная информация о моделях кластеров (ОЗУ, флэш, логика, интерфейсы), позволяющая создавать расширенный набор тестов.

В JTAG ProVision существует возможность импорта различных данных (кнопка «Import»). Это может быть информация о найденных в процессе тестирования платы дефектных цепях или полный отчёт о тестовом покрытии.

Использование программы JTAG Maps позволяет оценить доступность сигналов периферийного сканирования к цепям разрабатываемого устройства. Этот инструмент не укажет, какие из тестов выполнимы для кластеров – устройств, окружающих компоненты с поддержкой JTAG. Как же понять, возможно ли протестировать, например,

Рис. 4. Получение общей статистики по тестовому покрытию

микросхему оперативной памяти, подключённую к процессору, имеющему периферийное сканирование? Ответ прост: необходимо посмотреть все ли управляющие сигналы ОЗУ имеют хотя

бы оранжевый цвет. Также необходимо убедиться в наличии доступа хотя бы к части линий данных и адреса. Аналогично можно провести анализ доступности и к другим типам кластеров.

Программа JTAG Maps является отличным инструментом, помогающим обеспечить надлежащую тестируемость сложных цифровых устройств на ранних стадиях разработки.

**Светопроводник к Вашему успеху**

**Автоматизация**

**Автомобилестроение**

**Медицина**

**Световоды для SMD- и ТНТ-светодиодов**

**Особенности:**

- Световоды со степенью защиты IP68

- Диапазон температур: -40...+85°C

- Возможно изготовление заказных изделий

**ProCHIP**

POWERED BY PROSOFT

**ОФИЦИАЛЬНЫЙ ДИСТРИБЬЮТОР**

**АКТИВНЫЙ КОМПОНЕНТ ВАШЕГО БИЗНЕСА**

(495) 232-2522 • INFO@PROCHIP.RU • WWW.PROCHIP.RU

ВЕКТОРНЫЕ АНАЛИЗАТОРЫ ЦЕПЕЙ

# ПАНОРАМА

Диапазон частот от **0,3/10** МГц до **13,5/26,5** ГГц

Широкий динамический диапазон – до **145** дБ

Точные

измерения

по доступной

цене!

Широкий динамический диапазон и максимальная выходная мощность – вот, что делает **векторный анализатор цепей серии «Панорама»** превосходным устройством для измерения комплексных S-параметров линейных одно- и двухпортовых устройств, различных характеристик нелинейных цепей. Анализатор цепей «Панорама» демонстрирует беспрецедентное соотношение цены и технических характеристик, благодаря высокой скорости работы, компактности, а также набору различных опций и возможностей.

Получите скидку прямо сейчас по промокоду «Современная электроника». Не упустите свой шанс!

АО «НПФ «Микран»

пр-т Кирова, 51д, г. Томск, Россия, 634041

+7 3822 90-00-29 | +7 3822 41-34-03 | +7 3822 42-36-15 факс

mic@micran.ru

[www.micran.ru](http://www.micran.ru)