# Интерактивная трассировка в среде Altium Designer

## Часть 3. Правила и редактирование

Алексей Якубенко ([support@idstrade.com](mailto:support@idstrade.com))

В предыдущих частях статьи были рассмотрены основные принципы, инструменты и настройки интерактивной трассировки. В данной части будут описаны правила, которые непосредственно связаны с прокладкой проводников, а также инструменты редактирования проложенных проводников.

### ПРАВИЛА

Технология изготовления печатной платы (ПП) оказывает прямое влияние на такие её конструктивные параметры, как ширина проводников, зазоры между различными элементами топологии и геометрические параметры переходных отверстий (ПО). Современный учёт данных параметров в процессе разработки ПП может значительно сократить время проектирования и повысить его эффективность. В среде Altium Designer (AD) данные параметры задаются с помощью правил типа *Electrical → Clearance, Routing → Width, Manufacturing → Board Outline Clearance и Routing → Routing Via Style*.

Далее будет рассмотрена настройка правил указанных типов.

#### Правила типа *Electrical → Clearance*

Наиболее часто применяемый тип правил – *Electrical → Clearance*. Его

назначение состоит в определении величин зазоров между различными объектами токопроводящих слоёв.

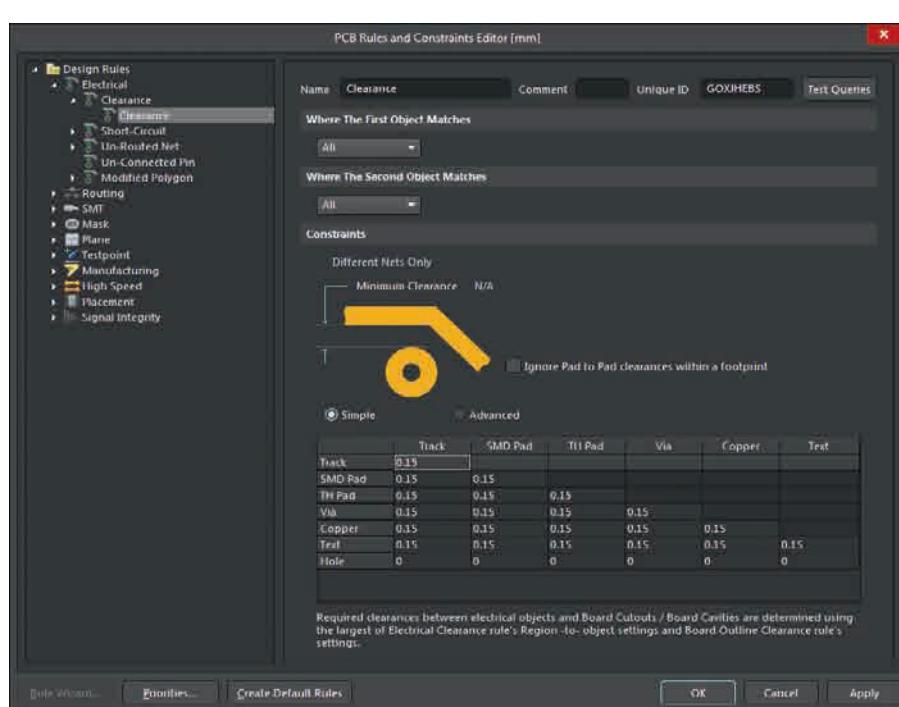

В окне редактора правил все правила данного типа сгруппированы в разделе *Electrical → Clearance* (см. рис. 1). Величины зазоров определяются с помощью опций, представленных в поле *Constraints*. Если величина зазоров должна быть одинакова для всех объектов топологии, то её достаточно задать с помощью опции *Minimum Clearance*. Правее схематичного изображения проводника находится пункт *Ignore Pad to Pad clearances within a footprint*. Выбор этого пункта отменяет проверку зазоров между контактными площадками (КП), которые относятся к одному посадочному месту (ПМ).

Если необходимо сформировать разные значения зазоров для разных объектов топологии, то сделать это мож-

но с помощью таблицы зазоров, расположенной чуть ниже. Каждая строка и каждый столбец таблицы соответствуют определённому объекту топологии. Зазор задаётся отдельно для каждой пары объектов. Для этого первым щелчком левой кнопки мыши (ЛКМ) выделяется ячейка, расположенная на пересечении строки одного объекта и столбца второго, а вторым щелчком она активируется, после чего вводится новое значение. На рисунке 1 отображён упрощённый вариант таблицы. Переход к расширенному варианту производится с помощью переключателя *Simple/Advanced*, расположенного над таблицей. Строки и столбцы таблицы зазоров соответствуют следующим объектам топологии:

- *Arc* (в расширенной таблице) – дуга;

- *Track* – отрезок (в расширенной таблице) или отрезок и дуга (в упрощённой таблице);

- *SMD Pad* – КП поверхностного монтажа;

- *TH Pad* – КП монтажа в отверстия;

- *Via* – ПО;

- *Copper* (в упрощённой таблице) – полигональные объекты;

- *Fill* (в расширенной таблице) – прямоугольная заливка;

- *Poly* (в расширенной таблице) – полигон;

- *Region* (в расширенной таблице) – регион;

- *Text* – текстовая строка;

- *Hole* – отверстие [1].

#### Правила типа *Routing → Width*

Не менее важный тип правил – *Routing → Width*: с помощью него определяются предельные и предпочтительные значения ширины проводников.

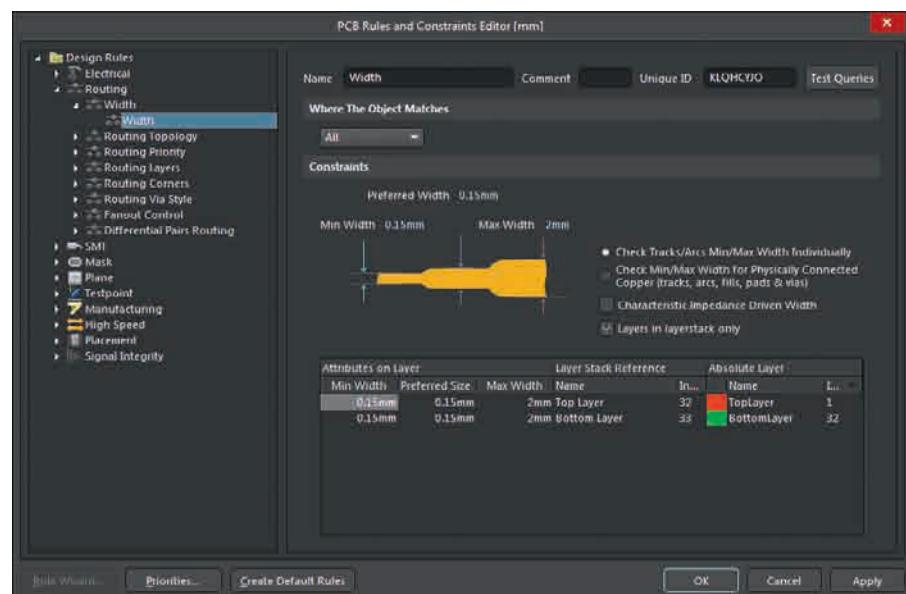

В окне редактора правил все правила данного типа сгруппированы в разделе *Routing → Width* (см. рис. 2). Настройка правила производится с помощью опций, представленных в поле *Constraints*. На схематичном изображении проводника имеются следующие основные опции:

- *Min Width* – минимально допустимая ширина проводника;

- *Preferred Width* – предпочтительная ширина проводника;

Рис. 1. Окно *Electrical → Clearance* в редакторе правил

- *Max Width* – максимально допустимая ширина проводника.

В нижней части области находится таблица, с помощью которой можно задать указанные значения отдельно для каждого слоя.

Правее схематичного изображения проводника можно найти переключатель режимов проверки ширины проводников; он имеет следующие положения:

- *Check Tracks/Arcs Min/Max Width Individually* – независимая проверка каждого отрезка и каждой дуги;

- *Check Min/Max Width for Physically Connected Copper (tracks, arcs, fills, pads & vias)* – проверка подключённых элементов топологии (отрезков, дуг, прямоугольных заливок, КП и ПО) с учётом прохождения тока.

Суть режима проверки проводников с учётом прохождения тока состоит в том, чтобы удостовериться в отсутствии на пути следования тока по проводящим линиям узких мест с шириной меньше указанной с помощью опции *Min Width* (в то же время не подключённые ни к каким цепям отрезки и дуги также проверяются по отдельности).

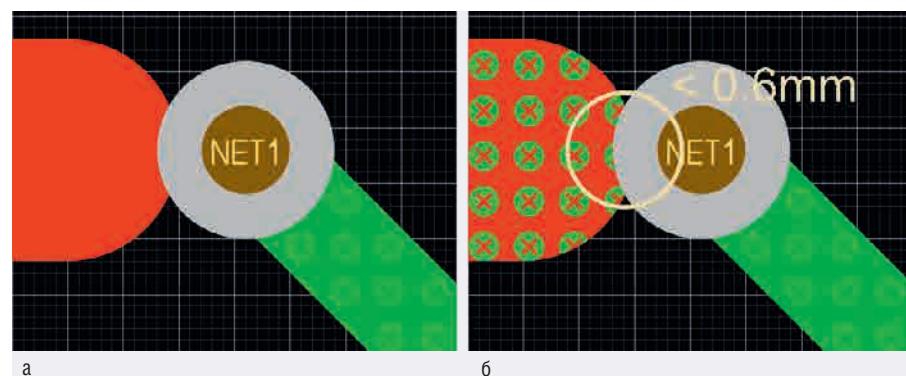

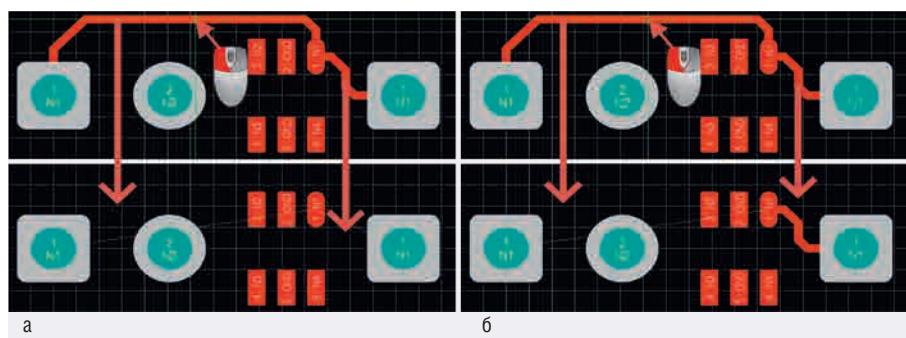

На рисунке 3 приведён пример, характеризующий разницу между двумя режимами проверки: на рисунке 3а представлен результат в режиме независимой проверки, а на рисунке 3б – в режиме проверки с учётом прохождения тока. В первом случае ошибка была найдена только в ширине проводника, расположенного на зелёном слое. Во втором случае было обнаружено, что на красном слое в месте соединения недоведённого проводника и ПО образуется узкое место с недостаточной шириной, выделенное в результате маркером ошибки.

Под переключателем режимов проверки расположен пункт *Characteristic Impedance Driven Width*, выбор которого переводит правило в режим определения ширины проводника в зависимости от комплексного сопротивления. Ещё ниже находится пункт *Layers in layerstack only*. При выборе этого пункта в таблице, расположенной в нижней части области, отображаются только те сигнальные слои, которые входят в стек текущей ПП. При снятии галочки выбора в таблице отобразятся все 32 доступных в среде AD сигнальных слоя [2].

#### Правила типа **Routing → Routing Via Style**

Правила типа *Routing → Routing Via Style* предназначены для определе-

Рис. 2. Окно **Routing → Width** в редакторе правил

Рис. 3. Режимы проверки ширины проводников: а) независимая проверка элементов топологии; б) проверка с учётом прохождения тока

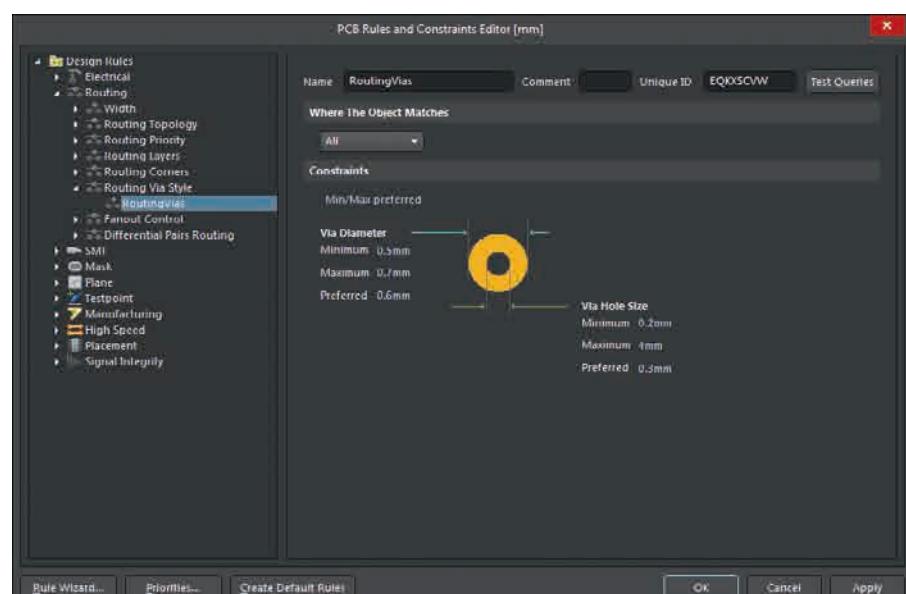

Рис. 4. Окно **Routing → Routing Via Style** в редакторе правил

ния предельных и предпочтаемого значений диаметров ПО и его КП. В окне редактора правил все правила данного типа сгруппированы в разделе *Routing → Routing Via Style*

(см. рис. 4). Настройка правила производится с помощью опций, представленных в поле *Constraints*. На схематичном изображении ПО имеются следующие основные опции:

Рис. 5. Окно Manufacturing → Board Outline Clearance в редакторе правил

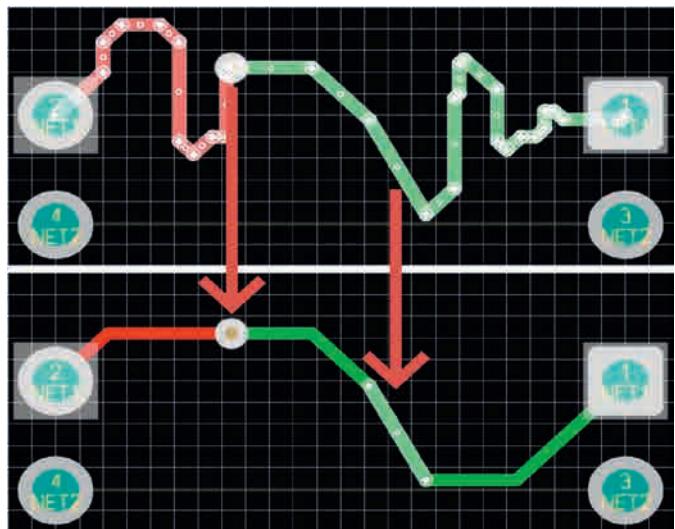

Рис. 6. Пример редактирования проводника за счёт удаления петли

- **Via Diameter:**

- *Minimum* – минимально допустимый диаметр КП ПО;

- *Maximum* – максимально допустимый диаметр КП ПО;

- *Preferred* – предпочтаемый диаметр КП ПО;

- **Via Hole Size:**

- *Minimum* – минимально допустимый диаметр ПО;

- *Maximum* – максимально допустимый диаметр ПО;

- *Preferred* – предпочтаемый диаметр ПО [3].

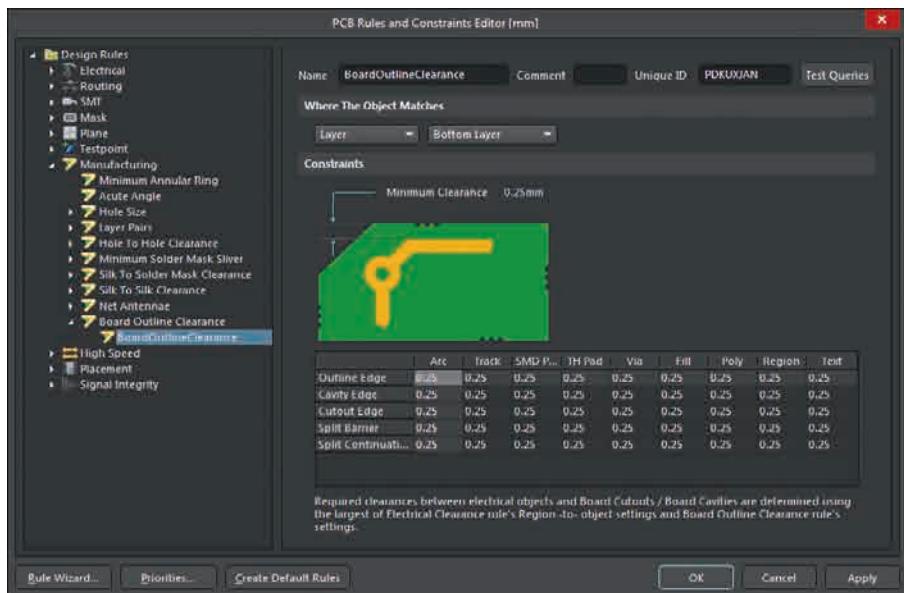

#### Правила типа Manufacturing → Board Outline Clearance

Не менее важный конструкторско-технологический параметр – минимальное расстояние от элементов топологии

до краёв ПП. За этот параметр отвечают правила типа *Manufacturing → Board Outline Clearance*. В окне редактора правил все правила данного типа сгруппированы в разделе *Manufacturing → Board Outline Clearance* (см. рис. 5).

Приёмы работы с правилами данного типа аналогичны приёмам работы с правилами типа *Electrical → Clearance*. Величины отступов определяются с помощью опций, представленных в поле *Constraints*. Если величина отступов всех элементов топологии от всех видов границ платы должна быть одинаковой, то её достаточно задать с помощью опции *Minimum Clearance*. Если же для разных элементов топологии или разных видов границ ПП необходимо определить разные значения отступов, то это можно сделать с

помощью расположенной ниже таблицы отступов. Каждая строка таблицы соответствует одному из типов границы ПП:

- *Outline Edge* – внешняя граница ПП;

- *Cavity Edge* – граница полости для расположения компонента внутри ПП;

- *Cutout Edge* – граница выреза в ПП;

- *Split Barrier* – граница разделения стеков слоёв;

- *Split Continuation* – продолжение границы разделения стеков слоёв.

- Каждый столбец таблицы соответствует определённому объекту топологии:

- *Arc* – дуга;

- *Track* – отрезок;

- *SMD Pad* – КП поверхностного монтажа;

- *TH Pad* – КП монтажа в отверстия;

- *Via* – ПО;

- *Fill* – прямоугольная заливка;

- *Poly* – полигон;

- *Region* – регион;

- *Text* – текстовая строка [4].

#### РЕДАКТИРОВАНИЕ ПРОВОДНИКОВ

Как в случае прокладки проводников, так и в случае их редактирования среда AD предоставляет разработчикам ряд удобных и эффективных инструментов по изменению топологии.

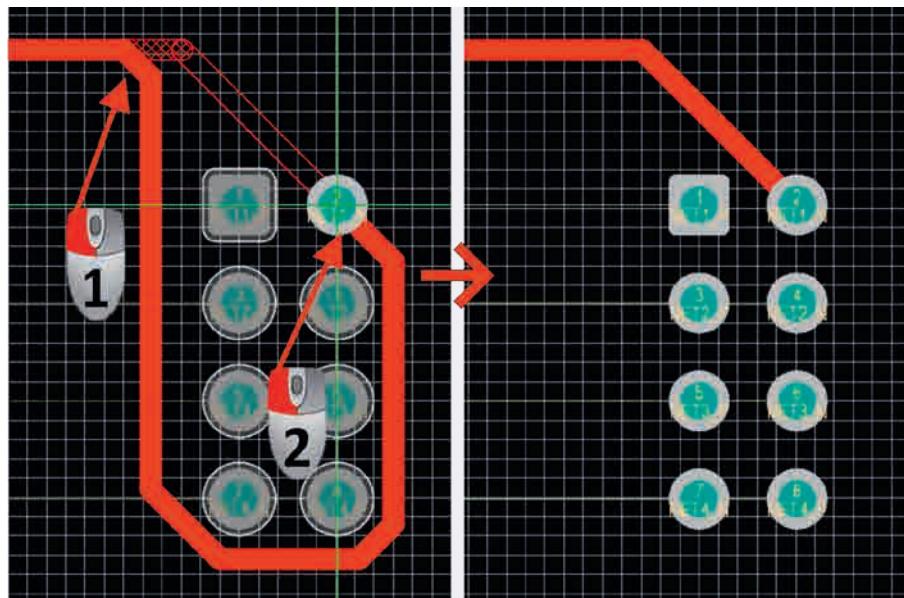

В первой части статьи были рассмотрены настройки *Automatically Remove Loops* и *Remove Net Antennas*, которые позволяют редактору ПП автоматически удалять петли и «антенны» [8]. Очевидно, что данный механизм представляет разработчикам удобнейший инструмент по редактированию проложенных проводников. Суть в том, что при необходимости изменить трассу проводника достаточно просто проложить новую трассу, которая будет начинаться и заканчиваться на элементах старой. В результате образуются одна или несколько петель. Редактор ПП избавится от этих петель за счёт удаления части старой трассы (см. рис. 6). Таким способом можно «перерисовать» как весь проводник, так и его часть.

Наиболее примитивный способ редактирования проложенных проводников – удаление старых трасс и прокладка новых. Можно удалить как один сегмент, предварительно выделив его ЛКМ, так и группу сегментов, выделив их сочетанием клавиш *Shift*+ЛКМ. Кроме того, можно выделить один из сегментов проводника и нажать клавишу *Tab* – в результате будут выделены все

последовательно сопряжённые сегменты, находящиеся на том же слое.

### **Un-Route**

Удалять вручную элементы проводников – дело достаточно неблагодарное, особенно когда речь идёт о большом количестве цепей. На этот случай предусмотрена группа команд *Un-Route*. Одноимённый пункт располагается в самом низу меню *Route*. Здесь доступны следующие команды:

- *All* (горячие клавиши  $U \rightarrow U \rightarrow A$ ) – полное удаление проводников всех цепей ПП;

- *Net* (горячие клавиши  $U \rightarrow U \rightarrow N$ ) – полное удаление проводника одной цепи;

- *Connection* (горячие клавиши  $U \rightarrow U \rightarrow C$ ) – удаление соединения;

- *Component* (горячие клавиши  $U \rightarrow U \rightarrow O$ ) – удаление всех подключённых к компоненту проводников;

- *Room* (горячие клавиши  $U \rightarrow U \rightarrow R$ ) – удаление всех цепей, относящихся к определённой области.

При выполнении любой из указанных команд происходит удаление отрезков и дуг, из которых состоят проводники, а также ПО. Полигональные объекты не удаляются.

Для полного удаления всех проводников ПП достаточно просто выполнить команду *Route → Un-Route → All*. В случае остальных команд после их запуска редактор ПП перейдёт в режим удаления, а курсор, в зависимости от настроек, примет вид большого или малого перекрестья под углом 90° или малого перекрестья под углом 45°. В данном режиме необходимо щёлкнуть ЛКМ по:

- сегменту проводника или контактной площадке – в случае удаления проводника или соединения;

- компоненту – в случае удаления подключённых к компоненту проводников;

- области – в случае удаления цепей, относящихся к определённой области.

Для выхода из режима удаления нужно щёлкнуть правой кнопкой мыши (ПКМ) или нажать клавишу *ESC*.

Различие между командами *Route → Un-Route → Net* и *Route → Un-Route → Connection* в том, что в первом случае происходит полное удаление всего проводника цепи, а во втором удаляется только соединение между двумя ближайшими конечными точками, например между двумя КП или между КП и концом недоведённого проводника.

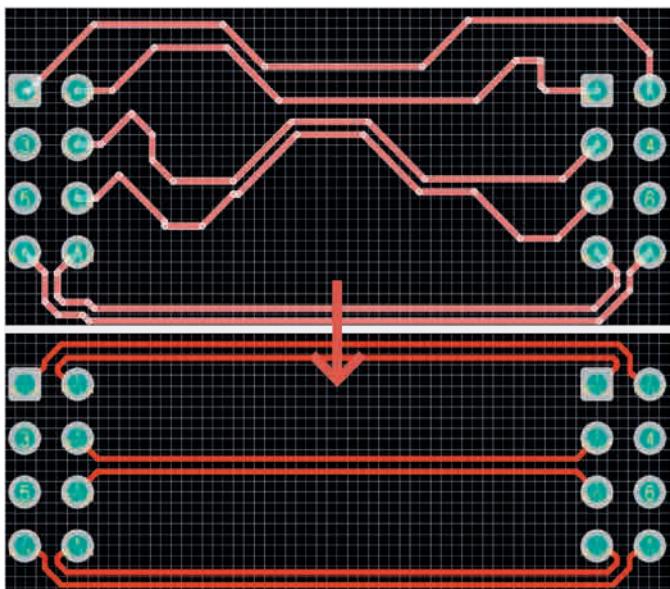

Рис. 7. Разница между командами: а) *Un-Route → Net*; б) *Un-Route → Connection*

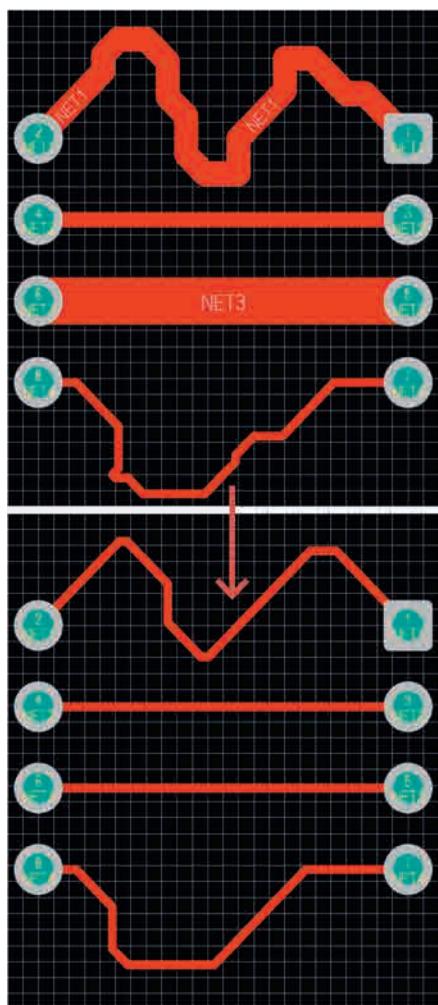

Рис. 8. Оптимизация отдельной цепи

На рисунке 7 приведены примеры, поясняющие данную разницу [5].

### **Gloss Selected**

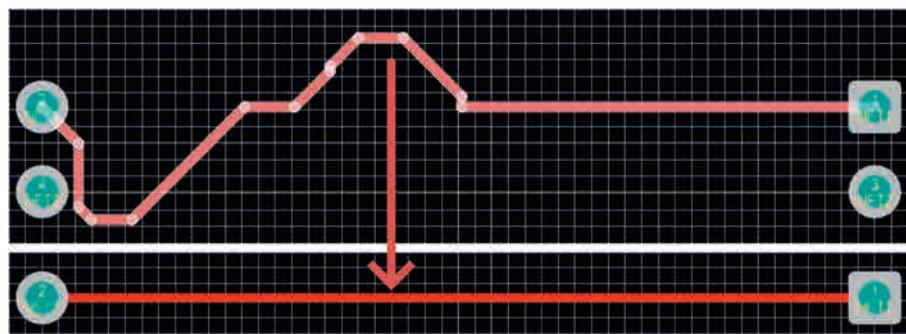

Ранее, в первой части статьи [8], мы уже рассматривали применение механизма *Gloss*. Напомним, *Gloss* представляет собой механизм оптимизации цепи, т.е. проекладки проводника таким образом, чтобы он имел наименьшую длину и наименьшее количество изгибов. В первой части речь шла о применении данного механизма в процессе прокладки нового проводника. Сейчас рассмотрим применение этого механизма для уже проложенных трасс цепей.

В общем случае для оптимизации уже проложенных проводников необходимо выполнить два действия:

1. Выбрать проводники или их части, которые необходимо оптимизировать.

2. Запустить команду *Route → Gloss Selected* (горячие клавиши  $U \rightarrow L$  или  $Ctrl + Alt + G$ ). Выбранные проводники или их части будут оптимизированы.

Механизм оптимизации *Gloss* применим к отдельному проводнику, дифференциальной паре или группе проводников. Более того, можно оптимизировать цепи как целиком, так и их фрагменты. Если необходимо оптимизировать проводник полностью, то для этого нужно выбрать все его сегменты (см. рис. 8). Чтобы оптимизировать фрагмент проводника, необходимо

выбрать только те сегменты, которые входят в соответствующую часть. Необходимо при этом иметь в виду, что при оптимизации фрагмента его крайние точки остаются на месте.

Можно также оптимизировать проводники, переходящие со слоя на слой или имеющие в своём составе перемычки, однако при этом перемычки и ПО остаются на месте. Кроме того, не оптимизируются сегменты, расположенные под произвольным углом (см. рис. 9). Необходимо обратить внимание, что при построении нового проводника среда AD использует только стандартные сегменты, расположенные под углами 45° и 90°.

При необходимости оптимизировать группу проводников перед запуском команды *Route → Gloss Selected* нужно также выбрать все сегменты всех оптимизируемых проводников.

Для оптимизации дифференциальных пар также необходимо выбирать все сегменты всех оптимизируемых проводников (см. рис. 10).

Однако здесь есть ряд нюансов, отличных от остальных случаев оптимизации. В данном случае редактор ПП «понимает», что он работает именно с дифференциальными парами, поэтому применяет механизмы, свойственные трассировке дифференциальных пар – система ориентируется на правила соответствующего типа, выполняет правильные отводы от КП. Кроме того, редактор пытается

Примечание: при оптимизации переходные отверстия и сегменты, расположенные под произвольным углом, остаются на месте

**Рис. 9. Оптимизация сегментов**

**Рис. 10. Оптимизация дифференциальных пар**

**Рис. 11. Применение команды *Route → Retrace Selected***

ализированные механизмы выравнивания длин всё же не применяются [6].

#### **Retrace Selected**

Ещё одним удобным инструментом корректировки проложенных проводников является команда *Route → Retrace Selected*. Её назначение в том, чтобы применить к выбранным проводникам или их фрагментам параметры ширины или зазоров, определённые соответствующими правилами как предпочтительные. Применение данной команды аналогично применению команды *Route → Gloss Selected*: сначала необходимо выбрать сегменты или проводники полностью, а потом выполнить команду (см. рис. 11).

Так же как и команда *Route → Gloss Selected*, команда *Route → Retrace Selected* применима к отдельным проводникам, группам проводников, дифференциальным парам и отдельным фрагментам проводников.

При работе с дифференциальными парами есть особенность: с помощью этой команды можно легко менять зазор в проложенной паре. Для этого нужно поменять его предпочтительное значение в соответствующем правиле, а потом применить команду.

В целом команды *Route → Gloss Selected* и *Route → Retrace Selected* подобны и даже используют один и тот же программный механизм. Основные отличия их в следующем:

- *Gloss* оставляет неизменной ширину проводника, а *Retrace* меняет её в соответствии со значением предпо-

читаемой ширины, прописанным в правилах;

- *Gloss* стремится максимально сократить длину проводника, что иногда приводит к радикальному изменению его трассы; *Retrace* лишь слегка корректирует проложенную трассу, делая её менее извилистой, если это необходимо ( обратите внимание на трассы цепей NET1 и NET4 на рисунке 11) [7].

Как видно, фактически, все основные инструменты трассировки являются интерактивными, следовательно, значительно облегчают труд разработчиков.

#### **ЛИТЕРАТУРА**

1. Altium. Documentation 2018. Clearance: [www.altium.com](http://www.altium.com)

2. Altium. Documentation 2018. Width: [www.altium.com](http://www.altium.com)

3. Altium. Documentation 2018. Routing Via Style: [www.altium.com](http://www.altium.com)

4. Altium. Documentation 2018. Board Outline Clearance: [www.altium.com](http://www.altium.com)

5. Altium. Documentation 2018. UnRoute: [www.altium.com](http://www.altium.com)

6. Altium. Documentation 2018. Gloss: [www.altium.com](http://www.altium.com)

7. Altium. Documentation 2018. Retrace: [www.altium.com](http://www.altium.com)

8. Якубенко А. Интерактивная трассировка в среде Altium Designer. Часть 1. Трассировка отдельной цепи. Современная электроника. 2018. № 3.

9. Якубенко А. Интерактивная трассировка в среде Altium Designer. Часть 2. Трассировка дифференциальных пар и групп цепей. Современная электроника. 2018. № 4.

# interlight

MOSCOW

powered by light + building

Международная выставка декоративного

и технического освещения, электротехники

и автоматизации зданий

**6–9 ноября 2018**

ЦВК «Экспоцентр»

Москва

Компоненты | **NEW!**

Декоративное

освещение

Техническое

освещение

LED-технологии

Интегрированные

системы безопасности | **NEW!**

Электрические

лампы

Электротехника

Автоматизация зданий /

Умный дом

messe frankfurt

[www.interlight-moscow.ru](http://www.interlight-moscow.ru)