## **Кремниевая и арсенид-галлий-алюминиевая** технология

### Часть 10. Концепция построения оптического процессора

Валерий Сведе-Швец (0000es@mail.ru), Владислав Сведе-Швец, Максим Зиновьев (Москва)

Десятая часть статьи продолжает рассказ о возможных способах построения оптических процессоров, реализующих структуру векторноматричных умножителей, и процессоров с мультиклеточной структурой. В статье показана концепция построения многопроцессорной аналоговой и цифровой векторно-матричной вычислительной архитектуры с наращиваемой 3D-платформой вычислительных ядер и оптоэлектронными многоканальными коммутаторами стандарта SpaceWire на основе электронной базы 3D М ФЭФ М (3D многоканальный фотон-электрон-фотонный модуль).

Кремниевая технология, применяемая сегодня для создания процессоров, приближается к своему пределу, и ей на смену приходит оптическая технология, разрабатываются оптические фотонные процессоры.

Оптическая технология, созданная на основе лазеров, фотодетекторов и оптических волокон, позволяет передавать информацию целыми массивами, многоканально или даже изображениями, используя разные сре-

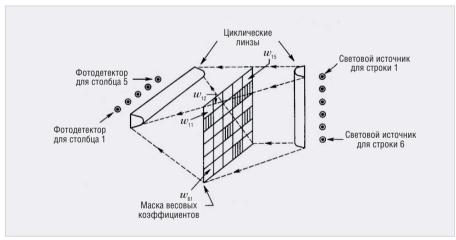

Рис. 76. Электронно-оптический векторно-матричный умножитель

Рис. 77. Процессор Multiclet R1

ды передачи, хранения и обработки информации. Обработка передаваемой информации во время её передачи через оптическую систему возможна практически мгновенно. На передачу информации оптическим путём тратится минимальная энергия, и при этом обеспечивается скрытность информации, поскольку оптический сигнал является однонаправленным и ничего не излучает в окружающую среду.

Все эти преимущества достигаются благодаря тому, что в качестве носителей информации используются фотоны, а не электроны.

Преимуществами оптических вычислителей являются:

- малое время срабатывания переключателей;

- высокий параллелизм;

- распространение сигнала со скоростью света;

- возможность прохождения большого количества световых сигналов по одной и той же области пространства без влияния друг на друга;

- практически полное отсутствие излучений во внешнюю среду.

#### Структура оптического векторно-матричного умножителя

Векторно-матричный умножитель это простейший по своей природе оптический процессор, имеющий средства для выполнения параллельного умножения матриц, которые требуются для работы большинства искусственных нейронных сетей. Параллельная природа вычислений в таком случае сохраняется и может быть описана математически в виде последовательных умножений вектора на матрицу - одна операция умножения в каждом слое. Таким образом, входной вектор умножается на матрицу весовых коэффициентов, образуя вектор NET. Затем к нему прикладывается функция активации F, образуя вектор OUT, являющийся выходом слоя:

$$NET = X \times W$$

$$OUT = F(NET),$$

где -NET вектор в виде строки, сформированный взвешенными суммами входов; OUT — выходной вектор; X — входной вектор; W — матрица весовых коэффициентов.

Существующие электронно-оптические нейронные сети работают со скоростью, ограниченной только доступными электронно-оптическими компонентами; время вычислений потенциально располагается в субнаносекундном диапазоне.

Система, обеспечивающая средства для выполнения параллельного умножения матриц, показана на рисунке 76. Размер матрицы – 6×5, при этом на выходе производится пятиэлементный вектор NET. Справа расположен столбец световых источников, лучи которых проходят через цилиндрические линзы; каждый луч освещает одну строку весовой маски. Таким образом, луч 1 освещает и  $w_{11} \, w_{12} \, w_{15}$ . При этом в качестве маски может быть использована, например, фотоплёнка или фотодиодная матрица, у которой каждый сектор пропорционален «весу». С левой стороны в случае с фотоплёнкой располагается вторая цилиндрическая линза, фокусирующая свет от каждого столбца маски на соответствующий фотодетектор, в результате чего световой поток на фотодетекторе 1 является суммой умножений световых интенсивностей на передаточную функцию столбца 1:

$$NET_{j} = \sum_{i} w_{ij} X_{i},$$

где  $NET_j$  – выход NE-нейрона j (выход фотодетектора j);  $w_{ij}$  – вес связи от нейрона i к нейрону j (величина, обратно пропорциональная прозрачности весовой маски в строке i, столбце j); X-i-я компонента входного вектора i (выход источника света i).

Таким образом, на выходе из системы получается вектор, равный произведению входного вектора и весовой матрицы. При этом данное матричное умножение выполняется параллельно и при использовании современных светоизлучающих диодов и фотодетекторов может быть выполнено менее чем за 1 нс. Кроме того, скорость умножения практически не зависит от размерности массива, что позволяет наращивать сети без существенного увеличения времени вычислений.

Существует перспективный метод, основанный на использовании жидко-

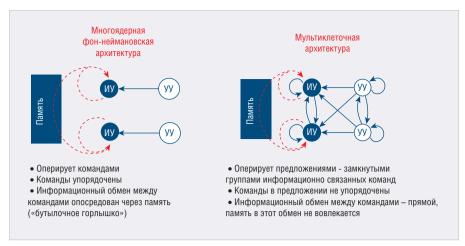

Примечание: ИУ – измерительное устройство, УУ – управляющее устройство.

Рис. 78. Мультиклеточная архитектура

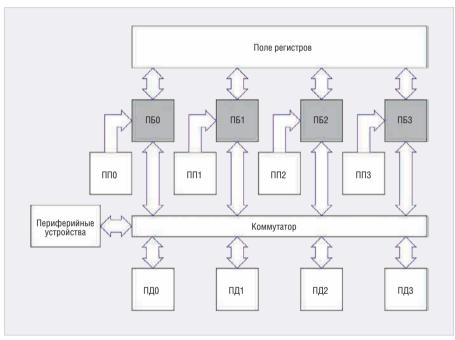

Примечание: ПП – память программ, ПД – память данных, ПБ – процессорный блок.

Рис. 79. Архитектура процессора Multiclet R1

кристаллической плёнки вместо фотографического негатива. Это позволяет изменять вес электронным способом в течение микросекунд.

#### Электронные процессоры с мультиклеточной архитектурой

Для решения задач, требующих одновременного их выполнения, был разработан принципиально новый процессор MULTICLET серии R (Reconfiguration), обладающий свойством динамической реконфигурации с мультиклеточной архитектурой. Данный тип изделия обладает возможностью динамической реконфигурации процессора в ходе выполнения алгоритма решения задач, в результате чего клетки ядра могут одновре-

менно заниматься решением разных задач.

Российский процессор MULTICLET R1 (см. рис. 77) является оригинальным процессором с универсальной не-фоннеймановской архитектурой (см. рис. 78).

Из представленной архитектуры (см. рис. 79) видно, что он имеет 4 процессорных ядра, общие регистровый файл и коммутатор, а также совместный доступ к памяти.

МULTICLET R1 работает на 100 МГц с числами одинарной точности single (32 бит) и, если упаковать комплексное число single, – точности в 64 бит (действительная и мнимая части по 32 бит). Если произвести умножение двух комплексных чисел за 1 такт, производительность будет равна 6 флоп/такт ( $(a+bi)\times(c+bd)+(ad+bc)\timesi$ ),

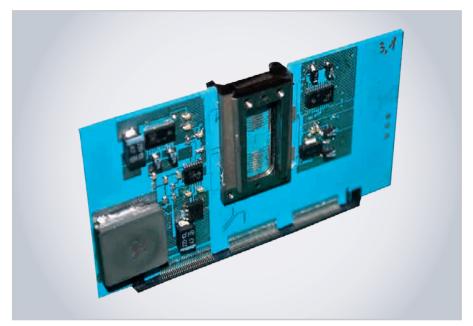

Рис. 80. Многослойная керамическая плата с двумя функциональными 3D М ФЗ СБИС Si и двумя 3D М ФЗ СБИС VCSEL и многоканальным электрическим разъёмом

соответственно, при 4 процессорных ядрах производительность будет 6×4×100 МГц = 2,4 Гфлопс. Максимальная скорость обмена данными в таком процессоре с внешним ПЗУ – 30 Мбит/с.

Мультиклеточное процессорное ядро выполняет задачи управления и обработки цифровых сигналов в приложениях, требующих минимального энергопотребления и высокой производительности. Оно может состоять из 4, 8, 16 или 64 клеток. Производительность для одной клетки типового мультиклеточного процессора с частотой до 5 ГГц составляет 10 Гфлопс — соответственно, 64-клеточный кристалл будет иметь 640 Гфлопс при потреблении 7,7 Вт электроэнергии.

Благодаря асинхронной и децентрализованной организации мультиклеточного процессора как на системном (между клетками (параллелизм)), так и внутриклеточном уровне (между блоками клетки (команды)) дополнительно обеспечиваются:

- минимизация номенклатуры и сложности объектов проектирования;

- уменьшение площади кристалла (децентрализованное управление);

- увеличение производительности и сокращение энергопотребления в несколько раз (эффективный вычислительный процесс);

- при реализации на одном кристалле десятков и сотен клеток – использование системы синхрони-

зации для каждой клетки индивидуально.

Многократное улучшение клеточных количественных характеристик, а также качественные отличия предлагаемой мультиклеточной архитектуры от известных моделей свидетельствуют о принципиальной новизне предлагаемого решения.

Кристалл сделан по технологическому процессу 180 нм. Тип корпуса LQFP-256 28×28 мм, разрядность 32/64, тактовая частота 100 МГц, производительность 2,4 Гфлопс.

# Построение многопроцессорной аналоговой и цифровой векторно-матричной вычислительной архитектуры

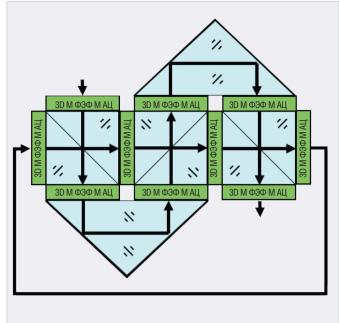

Концепция построения многопроцессорной аналоговой и цифровой векторно-матричной вычислительной архитектуры с наращиваемой 3D-платформой вычислительных ядер основана на элементной базе 3D М ФЭФ М и строится на правах внешнего вычислительного устройства – быстродействующего акселератора с управляющим микропроцессором TMS320C6455.

Базовой конструкцией 3D-матричной фотон-электрон-фотонной модульной процессорной системы – 3D М ФЭФ М ПС – является многослойная керамическая плата с двумя функциональными 3D М ФЭ СБИС Si и двумя 3D М ФЭ СБИС VCSEL и многоканальным электрическим разъёмом (см. рис. 80).

### Концепция построения 3D-матричной фотон-электронфотонной процессорной системы (аналоговой) – 3D М ФЭФ ПСА

Далее описывается принцип построения 3D М ФЭФ ПСА с однотактной операцией умножения вектора на матрицу на базе 3D М ФЭФ М АЦ с разрядностью АЦП 28 и многоканальным призменным мультиплексором.

В оптических операционных схемах, разработанных на базе 3D М ФЭФ М, применяется принцип многоканальной оптической коммутации на двух уровнях:

- 1. Внутренний в кристалле 3D М ФЭ СБИС Si применяется электронная коммутация выходных оптических сигналов матрицы пикселей.

- 2. Внешний с помощью оптического призменного мультиплексора осуществляется или прямая трансляция слайса матрицы оптических сигналов на приёмную 3D М ФЭФ М Si или коммутация слайса матрицы оптических сигналов с зеркальным отображением каналов слайса матрицы на другую приёмную 3D М ФЭФ M Si.

3D М ФЭФ ПСА строится на базе 3D М ФЭФ М АЦ с двумя 3D М ФЭ СБИС А/Ц и двумя 3D М ФЭ СБИС А/Ц.

### Вычисления вектор-матричных произведений на 3D M ФЭФ М ПСА

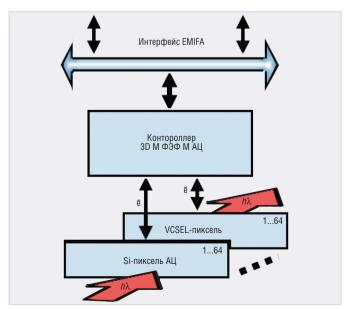

Аналоговые векторно-матричные потоковые вычислители – 3D М ФЭФ М ПСА – строятся на базе 3D М ФЭФ М АЦ, призменного мультиплексора и управляющего процессора ТМS320C6455. Структурная схема 3D М ФЭФ М АЦ приведена на рисунке 81.

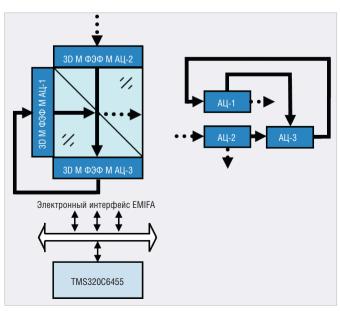

На рисунке 82 представлена структурная схема 3D М ФЭФ ПСА-1 для выполнения однотактного умножения 16-элементного входного вектора на матрицу размерностью 8×16 элементов с выводом результата 16-элементного вектора.

3D М Ф9Ф ПСА-1 реализована с помощью трёх 3D М Ф9Ф М АЦ с разрядностью АЦП  $2^8$  и многоканального призменного делителя.

Алгоритм вычислений. В 3D М ФЭФ М АЦ-1 значения данных вектора располагаются в выходной регистровой памяти матрицы горизонтально с заполнением всех строк выходного слайса матрицы и передаются через оптический многоканальный призменный делитель на входную приёмную матрицу 3D М ФЭФ М АЦ-3. Ины-

ми словами, в 3D М ФЭФ ПСА каждый пиксель горизонтально расположенного вектора выходной матрицы 3D М ФЭФ М АЦ-1 одновременно освещает выходной столбец весовой маски матрицы 3D М ФЭФ М АЦ-2 на приёмной матрице 3D М ФЭФ М АЦ-3 через оптический многоканальный призменный делитель. Таким образом, на приёмной матрице 3D М ФЭФ М АЦ-3 собираются два оптических потока: выходной оптический поток матрицы 3D М ФЭФ М АЦ-1 и выходной оптический поток матрицы 3D М ФЭФ М АЦ-1.

Операция заполнения всего поля матрицы значениями веса одного регистра эквивалентна операции размножения данных светового регистра с цилиндрической линзы, как в электронно-оптическом векторно-матричном умножителе (см. рис. 81).

В 3D М ФЭФ М АЦ-2 весами маски являются значения пикселей аналоговых оптических сигналов матрицы и переданный на вход приёмной матрицы 3D М ФЭФ М АЦ-3 через оптический многоканальный призменный делитель.

По команде производится передача аналоговых сигналов содержимого маски матрицы 3D М ФЭФ М АЦ-2 и векторов матрицы 3D М ФЭФ М АЦ-1 на приёмную матрицу 3D М ФЭФ М АЦ-3.

Таким образом, набор выходных интенсивностей световых потоков 3D М ФЭФ М АЦ-1 и 3D М ФЭФ М АЦ-2, принятых матрицей 3D М ФЭФ М АЦ-3, представляет собой результирующий вектор, равный произведению вход-

ного вектора и весовой матрицы, т.е. является суммой произведений световых интенсивностей матрицы и передаточной функции строки.

Результат операции умножения вектора на матрицу передаётся по оптическому или электрическому интерфейсу.

Технические характеристики оптического операционного устройства – 3D М ФЭФ МПА:

- скорость поступления информации для вычисления операции умножения вектора на матрицу – 166 МГц;

- разрядность входного вектора 16 элементов;

- разрядность матрицы 8×16 элементов:

- разрядность выходного вектора 16 элементов.

Модуль 3D М ФЭФ М АЦ работает с максимальной частотой 166 МГц. Это ограничение связано с максимальной частотой работы шины EMIFA управляющего процессора TMS320C6455, к которому подключён кристалл 3D М ФЭФ М АЦ.

Процессорная шина – это совокупность сигнальных линий, объединённых по своему назначению – данные, адреса, управление, – которые имеют определённые электрические характеристики и протоколы приёма/передачи информации. Процессорная шина является магистральным каналом между процессором/процессорами и всеми остальными устройствами, подключёнными к ней/к ним через контроллеры связи.

Существует возможность повышения частоты работы 3D M ФЭФ М для задач, в которых необходимо реализо-

вать быстрый буферизованный приём и/или передачу небольшой порции данных. В случае передачи данные должны быть предварительно загружены в регистры пикселей кристалла, а в случае приёма — читаться из регистров пикселей процессором уже после самой передачи данных через оптический интерфейс, т.е. кристалл 3D М ФЭФ М АЦ выступает в роли быстродействующего буфера.

Кристалл 3D М ФЭФ М АЦ имеет 2 независимых регистра данных для каждого пикселя: один для приёма и один для передачи данных. Размер каждого регистра — 8 бит, и последующий высокоскоростной приём 8 бит информации по оптическому интерфейсу.

Физические свойства кристалла 3D М ФЭФ М АЦ позволяют повысить его тактовую частоту до 1 ГГц при использовании только цифрового режима передачи данных через оптический интерфейс. Это позволяет осуществлять приём и передачу порции информации (8+8) по оптическому интерфейсу со скоростью до 1 ГГц на оптический канал. При этом обмен информацией с процессором TMS320C6455 всё так же производится на частоте работы шины EMIFA (которая не может быть повышена), т.е. с максимальной частотой 166 Мбит/с на канал. Отсюда видно, что повышение частоты кристалла 3D M ФЭФ М АЦ не требует увеличения быстродействия алгоритмов обработки информации самим процессором, т.к. количество информации, обрабатываемой процессором в единицу времени, не изменяется.

Рис. 81. Структурная схема 3D М ФЭФ М АЦ

Рис. 82. Структурная схема 3D М ФЗФ ПСА-1

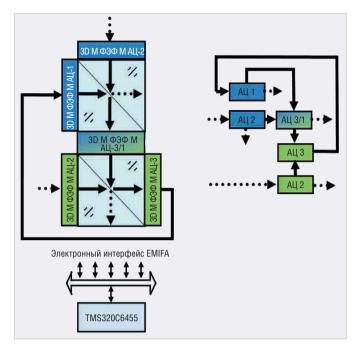

Рис. 83. Структурная схема 3D М ФЗФ ПСА-2

Рис. 84. Структурная схема 3D М ФЭФ ПСА-3

На рисунке 83 представлена структурная схема 3D М ФЭФ ПСА-2 с двумя соединёнными 3D М ФЭФ ПСА-1, последовательным выполнением умножения вектора на матрицу и функцией цикличности. Обратная многоканальная оптическая связь обеспечивает функцию цикличности операций умножения.

На рисунке 84 представлена структурная схема 3D М ФЭФ ПСА-3 с тремя соединёнными 3D М ФЭФ ПСА-1, последовательным выполнением умножения вектора на матрицу и функцией циклич-

ности. Обратная многоканальная оптическая связь обеспечивает функцию цикличности операций умножения.

Для увеличения производительности представленного оптического аналогового вычислительного устройства необходимо увеличение разрядности вектора и матрицы или организация многомодульности с цикличностью вычислений с сохранением результата предыдущих операций умножения вектора на матрицу.

Развитие первого направления ограничено ввиду высоких энерге-

тических затрат при большой размерности 3D М ФЭ СБИС VCSEL. Второе направление позволяет создавать высокопроизводительные векторноматричные 3D М ФЭФ ПСА большой разрядности.

В следующей части статьи речь пойдёт о концепции построения процессорной цифровой системы 3D М ФЭФ ПСЦ; будут представлены аналого-цифровые векторно-матричные потоковые вычислители 3D М ФЭФ ПСАЦ и масштабируемые системы с использованием процессора DSP TMS320C6455.

#### новости мира

### Эксперты GS Nанотесн заложили основы нового профстандарта для российской электронной отрасли

В октябре 2017 года Ассоциация разработчиков и производителей электроники объявила о создании рабочей группы по разработке профстандарта для одной из основных профессий электронной отрасли «Инженер-схемотехник электронной аппаратуры». Эксперты из GS Nanotech откликнулись на приглашение коллег и стали соавторами документа.

Созданный в сотрудничестве с экспертами GS Nanotech стандарт содержит описание функционала, требования к образованию, квалификации и навыкам инженеровсхемотехников электронной аппаратуры. Его принятие позволит разрабатывать новые инструменты для переподготовки кадров, курсы повышения квалификации

специалистов и даже образовательные программы вузов с учётом именно тех навыков, которые необходимы для работы на высокотехнологичном производстве микроэлектроники.

Сейчас проект обсуждается профессиональным сообществом. Ознакомиться с ним можно на сайте АРПЭ. После внесения корректировок документ направят на утверждение в Министерство труда и социальной защиты РФ.

Параллельно Ассоциация ведёт работу над стандартами «Инженер-конструктор электронной аппаратуры» и «Инженер-технолог производства электронной аппаратуры». Заявки на их разработку также были поданы в Минтруд России.

Пресс-служба GS Group

# ФГУП «МНИИРИП» представила торгово- информационную площадку «ЭКБ МАРКЕТ»

ФГУП «МНИИРИП», головная организация Минпромторга России по ЭКБ, представила торгово-информационную площадку отечественной электронной компонентной базы «ЭКБ МАРКЕТ» на 16-й международной выставке ChipEXPO.

Главная цель создания площадки – переориентация российского потребителя ЭКБ с иностранной компонентной базы на отечественную. Площадка предоставит удобный и простой доступ к базе отечественных компонентов, упростит заказ партий любого объёма, будет способствовать сокращению сроков поставки, обеспечит поиск и параметрическое сравнение компонентов по ключевым техническим характеристикам, а также сделает удобным их применение при проектировании и производстве аппаратуры за счёт наличия конструкторских библиотек для САПР.

Пользователи площадки — это потребители ЭКБ (инженеры-разработчики и закупщики) со стороны приборостроительных предприятий, производители и разработчики ЭКБ, поставщики и испытательные центры. Это будут как частные, так и государственные компании.

На площадке зарегистрировано уже более 160 участников; до конца 2018 года разработчики площадки ставят перед собой задачу увеличить их число до 300. Функциональные возможности площадки постоянно расширяются: на выставке был продемонстрирован механизм автоматической загрузки компонентов в каталог торгово-информационной площадки.

В дальнейшем площадка должна стать универсальной онлайн-платформой радиоэлектронной промышленности, позволяющей проводить онлайн-сделки с обеспечением гарантированных расчётов, обеспечивать интеграцию с информационными системами участников, сервис по шерингу производственных мощностей, а также анализировать рынок ЭКБ. Разработчики ставят задачу привлечь как можно больше экспертов от производителей отечественной ЭКБ, поставщиков и предприятий-потребителей к работе над расширением функционала платформы. В дальнейшем предполагается привлечь к данному информационному ресурсу производителей отечественного телекоммуникационного оборудования, вычислительной техники и других направлений радиоэлектронной аппаратуры.

Разработка площадки ведётся проектной командой организаций ФГУП «МНИИРИП», АО «ЦНИИ "Электроника"», ГК «Остек». В состав экспертной группы по разработке вошли представители потребителей, производителей и поставщиков ЭКБ, что позволяет учесть потребности всех заинтересованных сторон.

Команда разработчиков приглашает предприятия радиоэлектронной промыш-

ленности регистрироваться на торгово-информационной площадке «ЭКБ МАРКЕТ» и загружать данные по компонентам в каталог

www.ecbmarket.ru